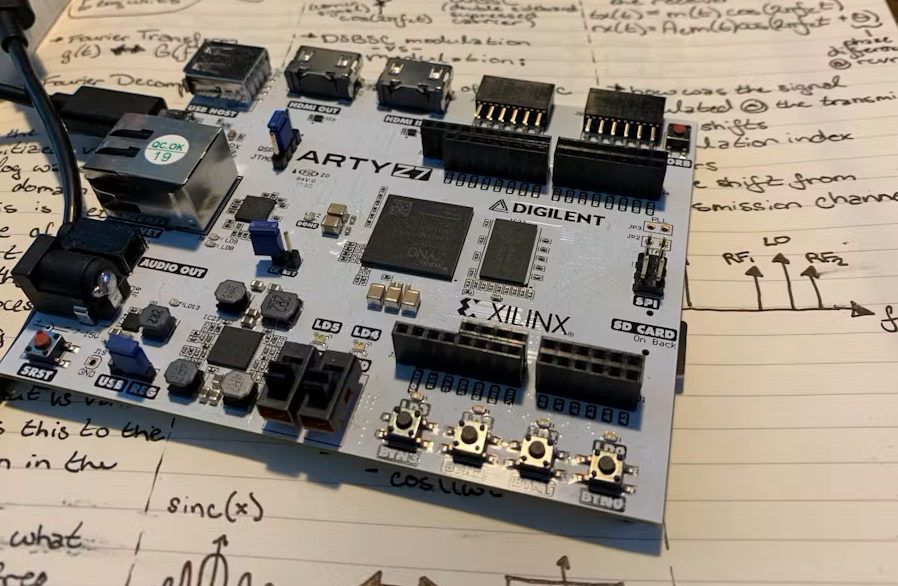

How to Use DDR Memory with FPGA for DSP Application?

Global electronic component supplier AMPHEO PTY LTD: Rich inventory for one-stop shopping. Inquire easily, and receive fast, customized solutions and quotes.

DDR (Double Data Rate) memory is commonly used in FPGA-based DSP (Digital Signal Processing) applications to store large datasets, filter coefficients, or real-time signal buffers. Here’s a step-by-step guide to integrating DDR memory with an FPGA for DSP.

1. Choose the Right DDR Memory & FPGA

DDR Memory Types

| Type | Speed (MHz) | Bandwidth | Use Case |

|---|---|---|---|

| DDR3 | 400-1066 | Moderate | General DSP, Video Processing |

| DDR4 | 800-3200 | High | High-performance DSP (Radar, AI) |

| LPDDR | 400-4266 | Low Power | Battery-powered DSP Systems |

| DDR2 | 200-533 | Legacy | Low-cost, older designs |

FPGA Requirements

-

DDR Memory Controller IP (Xilinx MIG, Intel UniPHY, Lattice DDR IP).

-

Sufficient I/O Pins (DQ, DQS, CLK, ADDR, CMD).

-

High-Speed Transceivers (if using DDR4/LPDDR4).

2. Hardware Design Considerations

PCB Layout Guidelines

-

Impedance Matching:

-

DDR traces (DQ, DQS) should be 50Ω single-ended or 100Ω differential.

-

Length-match data lanes (±50ps skew tolerance).

-

-

Power Delivery:

-

Use low-ESR decoupling capacitors near DDR power pins.

-

Follow FPGA vendor’s power sequencing requirements.

-

-

Routing:

-

Keep DQ/DQS/CLK traces short and away from noise sources.

-

Use fly-by topology for DDR3/4 address/command lines.

-

3. FPGA DDR Interface Setup

Step 1: Generate Memory Controller IP

-

Xilinx (Vivado):

-

Use Memory Interface Generator (MIG).

-

Configure:

-

Memory type (DDR3/DDR4).

-

Data width (e.g., 16-bit, 32-bit, 64-bit).

-

Clock speed (e.g., 800 MHz DDR3 → 400 MHz actual clock).

-

-

-

Intel (Quartus):

-

Use UniPHY DDR Controller.

-

Set up timing constraints (

set_input_delay,set_output_delay).

-

Step 2: Connect FPGA to DDR

-

Signals to Map:

-

DQ[0:N-1] (Data lines).

-

DQS (Data Strobe, differential for DDR3/4).

-

CLK/CLK# (Differential clock).

-

ADDR/CMD (Bank, Row, Column, RAS/CAS/WE).

-

ODT (On-Die Termination, DDR3/4 only).

-

Step 3: Add Timing Constraints

-

Define clock relationships (

create_clock,set_input_delay). -

Example (Xilinx):

create_clock -period 5.0 -name ddr_clk [get_ports ddr_clk_p] set_input_delay -clock ddr_clk -max 1.5 [get_ports ddr_dq*]

4. DSP Data Access Strategies

Burst Mode for Efficiency

-

DDR works best with sequential bursts (e.g., 8-word bursts for DDR3).

-

Example: Reading a 1024-point FFT buffer in 64-byte chunks.

Double Buffering (Ping-Pong)

-

Use two memory blocks to avoid stalls:

-

Buffer A: DSP writes new data.

-

Buffer B: DSP reads processed data.

-

DMA for High-Speed Transfer

-

Offload memory transfers to FPGA-based DMA.

-

Example: Xilinx AXI DMA IP for AXI4-stream ↔ DDR transfers.

5. DSP-Specific Optimizations

Memory Access Patterns

-

Block RAM (BRAM) Cache: Store frequently used coefficients.

-

Scatter-Gather DMA: For non-contiguous DSP data (e.g., sparse FIR filters).

Example: FIR Filter with DDR

-

Store coefficients in DDR.

-

Stream input samples via AXI4-Stream.

-

Multiply-Accumulate (MAC) in FPGA logic.

-

Write results back to DDR.

6. Debugging & Validation

Signal Integrity Checks

-

Use an oscilloscope to verify:

-

DQS-DQ alignment (eye diagram).

-

Clock jitter (<5% UI for DDR3).

-

FPGA Debug Tools

-

Xilinx ILA (Integrated Logic Analyzer) for DDR traffic.

-

Intel Signal Tap for monitoring read/write cycles.

Test Patterns

-

Write/read known patterns (e.g.,

0xAA55AA55) to verify correctness.

7. Common Pitfalls & Fixes

| Issue | Cause | Solution |

|---|---|---|

| Data corruption | Timing violations | Tighten constraints, adjust PCB routing |

| High latency | Non-sequential access | Use burst mode, prefetching |

| DDR not initializing | Power sequencing error | Check reset timing, voltage levels |

Conclusion

To use DDR memory with an FPGA for DSP:

-

Choose the right DDR type (DDR3/DDR4/LPDDR).

-

Design PCB carefully (impedance, length matching).

-

Generate a memory controller (MIG/UniPHY).

-

Optimize DSP access (burst mode, DMA, caching).

-

Debug with ILA/Signal Tap and signal integrity checks.

This approach ensures high-speed, reliable DSP processing with DDR memory.

Related Articles

- ·The best MCUs/MPUs for industrial humanoid robots

- ·What are the advantages and disadvantages of using SoCs in embedded systems?

- ·What are the differences between FPGA and DSP processors for signal processing?

- ·What is the Difference Between 8085 and 8086 Microprocessor?

- ·Digital Signal Processors vs x86 Architecture, What's the Different?

- ·How to become an FPGA engineer? Which FPGA board and program are suitable for beginners?

- ·How to Generate Low Clock Frequencies in FPGA?

- ·Application of Embedded Systems in Aerospace and Defense Fields

- ·Comparison of FPGA, ARM, STM32, and DSP Platforms